### OTP-Based 8-Bit Microcontroller with 10 bit ADC

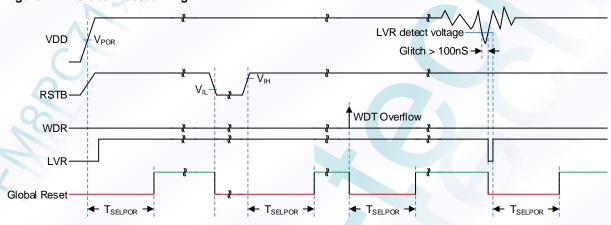

#### **Devices Included in this Data Sheet:**

• FM8PC713AMAEx: 8-pin OTP device FM8PC713AMAEL: 6-pin OTP device

#### **GENERAL DESCRIPTION**

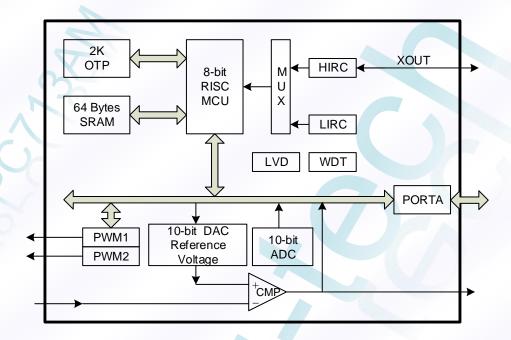

The FM8PC713AM is a low-cost, high speed, high noise immunity, OTP-based 8-bit CMOS microcontrollers. It employs a RISC architecture with only 39 instructions. All instructions are single cycle except for program branches which take two cycles. The easy to use and easy to remember instruction set reduces development time significantly.

#### **FEATURES**

- One clock per instruction cycle (1T, F<sub>CPU</sub>=16M<sub>HZ</sub> @ VDD≥ 2.4V).

- 2K on chip OTP and 64 x 8 bits on chip general purpose registers (SRAM).

- 6-level deep hardware stack

- Optional F<sub>IRC</sub> / (1, 2, 4, 8 or 16) MCU clock.

- Internal ±2% 16MHZ Oscillator.

- Internal oscillator 32 KHz free run clock for Slow / Green mode.

- Three real-time Timer/Counter with 3-bit programmable pre-scaler

- TM0: 8-bit Timer.

- PWM0: 16-bit PWM/Buzzer/Timer, output pin can be programmable.

- PWM1: 8-bit PWM/Buzzer/Timer, output pin can be programmable.

- Watch dog Timer.

- 6 I/O pins PORTA with independent direction control

- 15mA drive/sink current on any I/O pins (PA1 excepted).

- Soft-ware I/O pull-high or open-drain control.

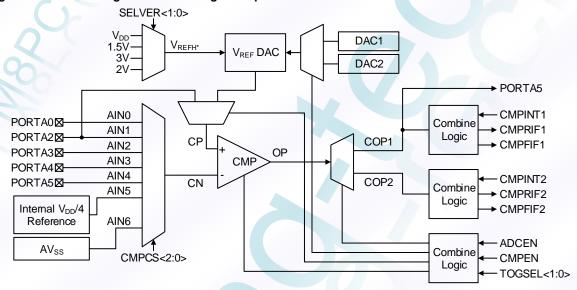

- Total 5 external channel and 2 internal channel 10bit AD converter

- Internal ±2% reference voltage 1.5V, 2.0V, 3.0V.

- Internal 1/4V<sub>DD</sub> and V<sub>SS</sub> Measurement.

- Optional Continues or Trigger mode to sample.

- Built-in voltage Comparator

- Low input offset voltage.

- Support 5 channel external input and internal 1/4V<sub>DD</sub>, V<sub>SS</sub> input comparison voltage.

- Five kinds of interrupt source: TM0, PWM0, PWM1 and LVDT, 6 external interrupt sources: PA5~PA0, Comparator and ADC.

- Built-in programmable 4 levels Low Voltage Detector (LVDT) (1.8V/2.0V/2.4V/3.0V).

- · Built-in Fixed Low Voltage Detect (2.0V).

This datasheet contains new product information. Feeling Technology reserves the rights to modify the product specification without notice. No liability is assumed as a result of the use of this product. No rights under any patent accompany the sales of the product.

### **BLOCK DIAGRAM**

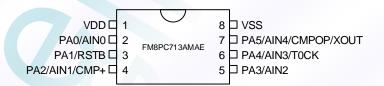

### **PIN CONNECTION**

Note that less than 8-pin MCU package types are not marketed in the following countries: USA, UK, Germany, The Netherlands, France and Italy.

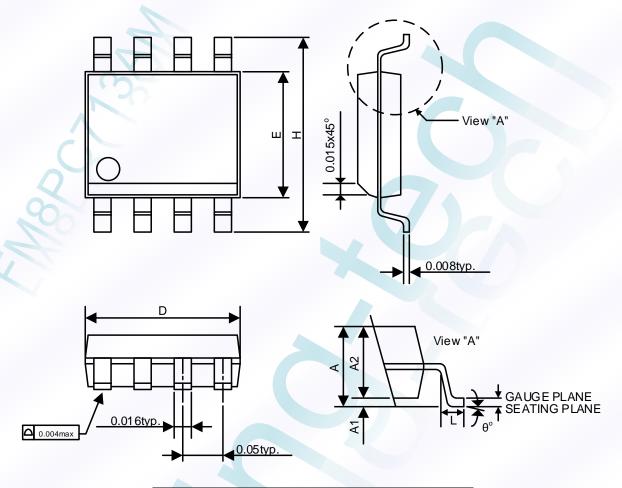

### SOT23-6

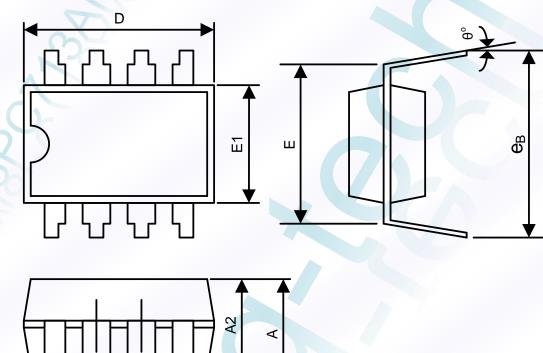

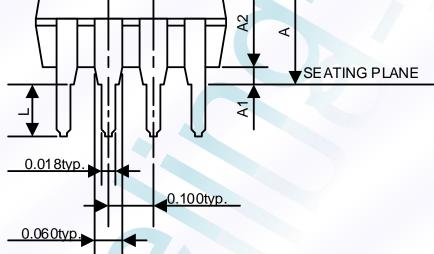

#### DIP/SOP8

### PIN DESCRIPTIONS

| Name                    | I/O | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA0/AIN0                | I/O | <ul> <li>Bi-direction I/O pin.</li> <li>Software controlled pull-high.</li> <li>A/D converter input.</li> <li>Programming Comparator Negative input.</li> <li>Programming PWM0/Buzzer0 or PWM1/Buzzer1 output.</li> </ul>                                                                                                                                                     |

| PA1/RSTB                | I/O | <ul> <li>Bi-direction I/O pin (Open-drain).</li> <li>Software controlled pull-high.</li> <li>System clear (RESET) input. Active low RESET to the device.</li> </ul>                                                                                                                                                                                                           |

| PA2/AIN1                | I/O | <ul> <li>Bi-direction I/O pin.</li> <li>Software controlled pull-high.</li> <li>A/D converter input.</li> <li>Programming Comparator Negative input.</li> <li>Fixed Comparator Positive input.</li> <li>Fixed PWM0/Buzzer0 differential output.</li> </ul>                                                                                                                    |

| PA3/AIN2                | I/O | <ul> <li>Bi-direction I/O pin.</li> <li>Software controlled pull-high.</li> <li>A/D converter input.</li> <li>Programming Comparator Negative input.</li> <li>Programming PWM0/Buzzer0 or PWM1/Buzzer1 output.</li> </ul>                                                                                                                                                     |

| PA4/AIN3/<br>T0CK       | I/O | <ul> <li>Bi-direction I/O pin.</li> <li>Software controlled pull-high.</li> <li>A/D converter input.</li> <li>External Clock input.</li> <li>Programming Comparator Negative input.</li> <li>Programming PWM0/Buzzer0 or PWM1/Buzzer1 output.</li> </ul>                                                                                                                      |

| PA5/AIN4/<br>CMPOP/XOUT | I/O | <ul> <li>Bi-direction I/O pin.</li> <li>Software controlled pull-high.</li> <li>A/D converter input.</li> <li>Comparator output.</li> <li>Up to 16M<sub>HZ</sub> F<sub>IRC</sub> external clock output.</li> <li>Programming Comparator Negative input.</li> <li>Programming PWM0/Buzzer0 or PWM1/Buzzer1 output.</li> <li>Fixed PWM1/Buzzer1 differential output.</li> </ul> |

| V <sub>DD</sub>         | -   | Positive supply.                                                                                                                                                                                                                                                                                                                                                              |

| Vss                     | - 7 | Ground.                                                                                                                                                                                                                                                                                                                                                                       |

Legend: I=input, O=output, I/O=input/output.

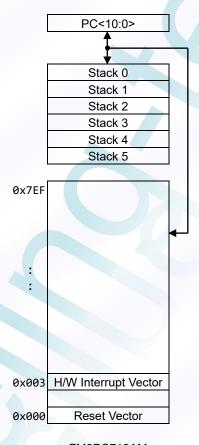

### 1.0 MEMORY ORGANIZATION

FM8PC713AM memory is organized into program memory and data memory.

### 1.1 Program Memory Organization

The FM8PC713AM have a 11-bit Program Counter capable of addressing a 2K program memory space.

The RESET vector for the FM8PC713AM is at 0x000.

The H/W interrupt vector is at 0x003.

FM8PC713AM supports all OTP area CALL/GOTO instructions without page.

Figure 1.1: Program Memory Map and STACK

FM8PC713AM

Note: Address  $0x7F0 \sim 0x7FF$  Reserved for Configuration word.

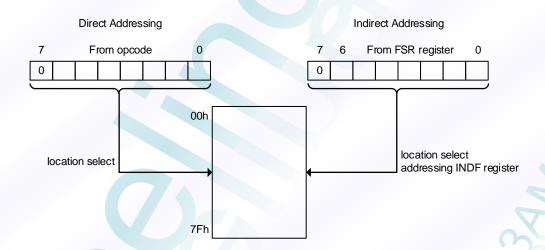

### 1.2 Data Memory Organization

Data memory is composed of Special Function Registers and General Purpose Registers.

The General Purpose Registers are accessed either directly or indirectly through the FSR register.

The Special Function Registers are registers used by the CPU and peripheral functions to control the operation of the device.

Table 1.1: Registers File Map for FM8PC713AM

| Address     | Description               |

|-------------|---------------------------|

| 0x00        | INDF                      |

| 0x02        | PCL                       |

| 0x03        | STATUS                    |

| 0x04        | FSR                       |

| 0x05        | PORTA                     |

| 0x07        | PAIE                      |

| 0x09        | PACON                     |

| 0x0B        | INTEN                     |

| 0x0C        | INTFLAG                   |

| 0x0E        | TM0                       |

| 0x0F        | TMOCON                    |

| 0x10        | TØRLD                     |

| 0x11        | WDT                       |

| 0x12        | PCON                      |

| 0x13        | CLKCFG                    |

| 0x14        | PWMØCON                   |

| 0x15        | PWM0CR                    |

| 0x16        | PØTMLB                    |

| 0x17        | POTMDTLB                  |

| 0x18        | РОТМНВ                    |

| 0x19        | POTMDTHB                  |

| 0x20        | PWM1CON                   |

| 0x21        | PWM1CR                    |

| 0x22        | P1TM                      |

| 0x23        | P1TMDT                    |

| 0x24        | BZS                       |

| 0x28        | ADCON1                    |

| 0x29        | ADCON2                    |

| 0x30        | ADCHB                     |

| 0x31        | ADCLB                     |

| 0x32        | ADCON3                    |

| 0x35        | CMPCON1                   |

| 0x36        | DACR1HB                   |

| 0x37        | DACR1LB                   |

| 0x38        | CMPCON2                   |

| 0x39        | DACR2HB                   |

| 0x3A        | DACR2LB                   |

| 0x40 ~ 0x7F | General Purpose Registers |

| 0x08 | PAMODE0 |

|------|---------|

| 0x09 | PAMODE1 |

0x17 POTMPRLB

0x19 POTMPRHB

0x23 P1TMPR

Table 1.2: The Registers Controlled by IOST or IOSTR Instructions

| Address     | Name 🦴      | B7 | В6                                           | B5        | B4          | В3           | B2          | B1     | В0     |  |  |  |  |

|-------------|-------------|----|----------------------------------------------|-----------|-------------|--------------|-------------|--------|--------|--|--|--|--|

| I/O PAD Mod | /O PAD Mode |    |                                              |           |             |              |             |        |        |  |  |  |  |

| 0x08 (r/w)  | PAMODE0     | -  | -                                            | PAMD05    | PAMD04      | PAMD03       | PAMD02      | PAMD01 | PAMD00 |  |  |  |  |

| 0x09 (r/w)  | PAMODE1     | -  | -                                            | PAMD15    | PAMD14      | PAMD13       | PAMD12      | PAMD11 | PAMD10 |  |  |  |  |

| PWM         |             |    |                                              |           |             |              |             |        |        |  |  |  |  |

| 0x17 (r/w)  | P0TMPRLB    |    | F                                            | PWM0 Peri | od cycle pr | e-set low-b  | yte registe | r      |        |  |  |  |  |

| 0x19 (r/w)  | POTMPRHB    |    | PWM0 Period cycle pre-set high-byte register |           |             |              |             |        |        |  |  |  |  |

| 0x23 (r/w)  | P1TMPR      |    |                                              | PWM1      | Period cyc  | le pre-set r | egister     |        |        |  |  |  |  |

Legend: - = unimplemented, read as '0'.

| Table 1.3: Op | erational Re | gisters Ma | р           |                  |              |              |              |              |         |

|---------------|--------------|------------|-------------|------------------|--------------|--------------|--------------|--------------|---------|

| Address       | Name         | B7         | В6          | B5               | B4           | B3           | B2           | B1           | B0      |

| Basic         |              |            |             |                  |              |              |              |              |         |

| 0x00 (r/w)    | INDF         | Use        | es contents | of FSR to        | address da   | ata memory   | (not a phy   | sical regist | ter)    |

| 0x02 (r/w)    | PCL          |            |             |                  | _ow order 8  | 3 bits of PC |              |              |         |

| 0x03 (r/w)    | STATUS       | -          | -           | FRP              | TO           | PD           | Z            | DC           | С       |

| 0x04 (r/w)    | FSR          | _          |             | Inc              | direct data  | memory ad    | dress poin   | ter          |         |

| I/O PAD & I/O | Interrupt C  | ontrol     |             |                  |              |              |              |              |         |

| 0x05 (r/w)    | PORTA        | -          | -           | PA5              | PA4          | PA3          | PA2          | PA1          | PA0     |

| 0x07 (r/w)    | PAIE         | -          | -           | PAIE5            | PAIE4        | PAIE3        | PAIE2        | PAIE1        | PAIE0   |

| 0x09 (r/w)    | PACON        | =          | -           | PACON5           | PACON4       | PACON3       | PACON2       | PACON1       | PACON0  |

| Interrupt     |              |            |             |                  |              |              |              |              |         |

| 0x0B (r/w)    | INTEN        | GIE        | -           | -                | LVDTSVIE     | LVDT20IE     | -            | -            | TM0IE   |

| 0x0C (r/w)    | INTFLAG      | -          | PAIF        | -                | LVDTSVIF     | LVDT20IF     | -            | -            | TM0IF   |

| Timer0        |              |            |             |                  |              |              |              |              |         |

| 0x0E (r)      | TM0          |            |             | 8-b              | it real time | clock/coun   | ter          |              |         |

| 0x0F (r/w)    | TMØCON       | TM0EN      | -           | TM0PS2           | TM0PS1       | TM0PS0       | TM0CKS1      | TM0CKS0      | -       |

| 0x10 (r/w)    | TØRLD        |            |             | TM0              | Compare      | Pre-set regi | ister        |              |         |

| System        |              |            |             |                  |              |              |              |              |         |

| 0x11 (r/w)    | WDT          | WDTE       | WDTSL       | WDTPS2           | WDTPS1       | WDTPS0       | LVRSL        | -            | -       |

| 0x12 (r/w)    | PCON         | -          | GRN_MD      | LVDIS            | RSTSL1       | RSTSL0       | UGMD         | LVDTSV       | LVDT20  |

| 0x13 (r/w)    | CLKCFG       | SELCLK2    | SELCLK1     | SELCLK0          | CLKSW        | -            | INCODS       | EXOSEN       | IRCEN   |

| PWM0          |              |            |             |                  |              |              |              |              |         |

| 0x14 (r/w)    | PWM0CON      | P0INTSL    | -           | LPTS0            | ENLP0        | P0CKS1       | P0CKS0       | P00SEL1      | P00SEL0 |

| 0x15 (r/w)    | PWM0CR       | PWM0EN     | P00UTS      | PØTPS2           | PØTPS1       | P0TPS0       | P0TMEN       | P0TMIE       | P0TMIF  |

| 0x16 (r)      | P0TMLB       |            |             | PWM              | real-time    | counter low  | /-byte       |              |         |

| 0x17 (r/w)    | P0TMDTLB     |            |             | PWM0 Du          | ty cycle pre | e-set low-by | te register  |              |         |

| 0x18 (r)      | РОТМНВ       |            | A = A       | PWMC             | real-time    | counter higl | n-byte       |              |         |

| 0x19 (r/w)    | P0TMDTHB     |            |             | PWM0 Dut         | y cycle pre  | -set high-by | /te register |              |         |

| PWM1          |              |            |             |                  |              |              |              |              |         |

| 0x20 (r/w)    | PWM1CON      | P1INTSL    | -           | LPTS1            | ENLP1        | P1CKS1       | P1CKS0       | P10SEL1      | P10SEL0 |

| 0x21 (r/w)    | PWM1CR       | PWM1EN     | P10UTS      | P1TPS2           | P1TPS1       | P1TPS0       | P1TMEN       | P1TMIE       | P1TMIF  |

| 0x22 (r)      | P1TM         |            |             | P                | WM1 real-    | time counte  | r            |              |         |

| 0x23 (r/w)    | P1TMDT       |            | 7 / 1       | PWM <sup>2</sup> | Duty cycle   | e pre-set re | gister       |              |         |

| 0x24 (r/w)    | BZS          | BZS1       | BZS0        | LVDTS1           | LVDTS0       | -            |              | -            | -       |

| ADC/DAC/Co    | mparator     |            |             |                  |              | 1            |              |              |         |

| 0x28 (r/w)    | ADCON1       | ADCEN      | ADCST       | CHSEL2           | CHSEL1       | CHSEL0       | ADCSR2       | ADCSR1       | ADCSR0  |

| 0x29 (r/w)    | ADCON2       | ADCIE      | ADCIF       | -                | ADCNT        | ADCLS        | ADCTCK       | SELVER1      | SELVER0 |

| 0x30 (r)      | ADCHB        | ADB9       | ADB8        | ADB7             | ADB6         | ADB5         | ADB4         | ADB3         | ADB2    |

| 0x31 (r)      | ADCLB        | -          | -           | -                | -            | -            | -/           | ADB1         | ADB0    |

| 0x32 (r/w)    | ADCON3       | -          | -           | -                | INEN4        | INEN3        | INEN2        | INEN1        | INEN0   |

| Address    | Name    | В7      | B6    | B5     | B4      | В3      | B2      | B1      | В0      |

|------------|---------|---------|-------|--------|---------|---------|---------|---------|---------|

| 0x35 (r/w) | CMPCON1 | CMPEN   | COP1  | CMPIE1 | CMPRIF1 | CMPFIF1 | CMPCS2  | CMPCS1  | CMPCS0  |

| 0x36 (r/w) | DACR1HB | DA1B9   | DA1B8 | DA1B7  | DA1B6   | DA1B5   | DA1B4   | DA1B3   | DA1B2   |

| 0x37 (r/w) | DACR1LB | -       | -     | I      | -       | -       | -       | DA1B1   | DA1B0   |

| 0x38 (r/w) | CMPCON2 | CMPINT1 | COP2  | CMPIE2 | CMPRIF2 | CMPFIF2 | CMPINT2 | TOGSEL1 | TOGSEL0 |

| 0x39 (r/w) | DACR2HB | DA2B9   | DA2B8 | DA2B7  | DA2B6   | DA2B5   | DA2B4   | DA2B3   | DA2B2   |

| 0x3A (r/w) | DACR2LB | -       | -     | -      | -       | -       |         | DA2B1   | DA2B0   |

Legend: - = unimplemented, read as '0'.

### 2.0 FUNCTIONAL DESCRIPTIONS

### 2.1 Operational Registers

### 2.1.1 INDF (Indirect Addressing Register)

| Read/Wr | ite-POR | R/W-0 | R/W-0       | R/W-0     | R/W-0      | R/W-0      | R/W-0      | R/W-0        | R/W-0 |

|---------|---------|-------|-------------|-----------|------------|------------|------------|--------------|-------|

| Address | Name    | В7    | В6          | B5        | В4         | В3         | B2         | B1           | В0    |

| 0x00    | INDF    | Use   | es contents | of FSR to | address da | ata memory | (not a phy | sical regist | ter)  |

The INDF Register is not a physical register. Any instruction accessing the INDF register can actually access the register pointed by FSR Register. Reading the INDF register itself indirectly (FSR="0x00") will read 0x00. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected).

The bits 6-0 of FSR register are used to select up to 128 registers (address:  $0x00 \sim 0x7F$ ).

### **Example 2.1: INDIRECT ADDRESSING**

- Register file 0x48 contains the value 0x10

- Register file 0x49 contains the value 0x0A

- Load the value 0x48 into the FSR Register

- A read of the INDF Register will return the value of 0x10

- Increment the value of the FSR Register by one (@FSR=0x49)

- A read of the INDF register now will return the value of 0x0A.

Figure 2.1: Direct/Indirect Addressing

#### 2.1.2 PCL (Low Byte of Program Counter) & Stack

| Read/Wr | Read/Write-POR |    | R/W-0                  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------|----------------|----|------------------------|-------|-------|-------|-------|-------|-------|--|

| Address | Name           | B7 | В6                     | B5    | B4    | В3    | B2    | B1    | В0    |  |

| 0x02    | PCL            |    | Low order 8 bits of PC |       |       |       |       |       |       |  |

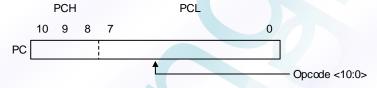

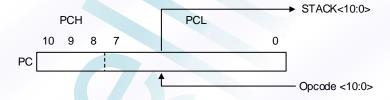

FM8PC713AM device has a 11-bit wide Program Counter (PC) and six-level deep 11-bit hardware push/pop stack. The low byte of PC is called the PCL register. This register is readable and writable. The high byte of PC is called the PCH register. This register contains the PC<10:8> bits and is unable to readable or writable. All updates to the PCH register go through the CALL or GOTO instruction. As a program instruction is executed, the Program Counter will contain the address of the next program instruction to be executed. The PC value is increased by one, every instruction cycle, unless an instruction changes the PC.

For a GOTO instruction, the PC<10:0> is provided by the GOTO instruction word. The PCL register is mapped to PC<7:0>.

For a CALL instruction, the PC<10:0> is provided by the CALL instruction word. The next PC will be loaded (PUSHed) onto the top of STACK. The PCL register is mapped to PC<7:0>.

For a RETIA, RETFIE, or RETURN instruction, the PC are updated (POPed) from the top of STACK. The PCL register is mapped to PC<7:0>.

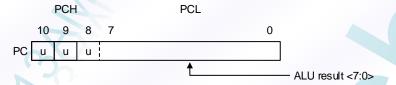

For any instruction where the PCL is the destination, the PC<7:0> is provided by the instruction word or ALU result.

Figure 2.2: Loading of PC in Different Situations

Situation 2: CALL Instruction

Situation 3: RETIA, RETFIE, or RETURN Instruction

#### Situation 4: Instruction with PCL as destination

### 2.1.3 STATUS (Status Register)

| Read/Write-POR |        | -  | -  | R/W-0 | R-# | R-# | R/W-0 | R/W-0 | R/W-0 |

|----------------|--------|----|----|-------|-----|-----|-------|-------|-------|

| Address        | Name   | В7 | В6 | B5    | B4  | В3  | B2    | B1    | В0    |

| 0x03           | STATUS | -  | -  | FRP   | TO  | PD  | Z     | DC    | С     |

Legend: - = unimplemented, read as '0', # = refer Table 2.8 for detail description.

This register contains the arithmetic status of the ALU, the RESET status.

If the STATUS Register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS Register as destination may be different than intended. For example, CLRR STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS Register as 000u u1uu (where u = unchanged).

C: Carry/borrow bit.

ADDAR, ADDIA

- = 1, Carry occurred.

- = 0, No Carry occurred.

SUBAR, SUBIA

- = 1, No borrow occurred.

- = 0, Borrow occurred.

Note: A subtraction is executed by adding the two's complement of the second operand. For rotate (RRR, RLR) instructions, this bit is loaded with either the high or low order bit of the source register.

DC: Half carry/half borrow bit.

ADDAR, ADDIA

- = 1, Carry from the 4th low order bit of the result occurred.

- = 0, No Carry from the 4th low order bit of the result occurred.

SUBAR, SUBIA

- = 1, No Borrow from the 4th low order bit of the result occurred.

- = 0, Borrow from the 4th low order bit of the result occurred.

**Z**: Zero bit.

- = 1, The result of a logic operation is zero.

- = 0, The result of a logic operation is not zero.

PD: Power down flag bit.

- = 1, after power-up or by the CLRWDT instruction.

- = 0, by the SLEEP instruction.

**TO**: Time overflow flag bit.

- = 1, after power-up or by the CLRWDT or SLEEP instruction.

- = 0, a watch-dog time overflow occurred.

FRP: From Register/Pin select bit.

- = 1, When BSR/BCR instruction execute, the other bit of updated from pin.

- = 0, When BSR/BCR instruction execute, the other bit of updated from register.

### 2.1.4 FSR (Indirect Data Memory Address Pointer)

| Read/Wr | ite-POR | -  | R/W-0 | R/W-0 | R/W-0         | R/W-0     | R/W-0      | R/W-0 | R/W-0 |

|---------|---------|----|-------|-------|---------------|-----------|------------|-------|-------|

| Address | Name    | В7 | В6    | B5    | B4            | В3        | B2         | B1    | В0    |

| 0x04    | FSR     | _  |       | Inc   | direct data ı | memory ad | dress poin | ter   |       |

Legend: - = unimplemented, read as '0'.

**Bit6:Bit0**: Select registers address in the indirect addressing mode. See section 2.1.1 for detail description on page 8.

### 2.1.5 PORTA (Port Data Register)

| Read/Write-POR |       | -  | -  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|----------------|-------|----|----|-------|-------|-------|-------|-------|-------|

| Address        | Name  | В7 | В6 | B5    | B4    | В3    | B2    | B1    | В0    |

| 0x05           | PORTA | -  | /- | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   |

Legend: - = unimplemented, read as '0'.

Reading the port (PORTA register) reads the status of the pins independent of the pin's input/output modes. Writing to these ports will write to the port data latch.

PORTA is 6-bit port data Registers.

PA5:PA0: PORTA I/O pin.

= 1, Port pin is high level.

= 0, Port pin is low level.

Note: PA1 pin is open-drain output only. If PAMODE0<1> & PAMODE1<1> = "1,1", and PA1 bit is set to "1", the PA1 pin will be float. See section 2.2 block diagram for detail description on page 28.

#### 2.1.6 PAIE (PORTA Interrupt Control Register)

| Read/Write-POR |      | -  | -  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|----------------|------|----|----|-------|-------|-------|-------|-------|-------|

| Address        | Name | В7 | В6 | B5    | B4    | В3    | B2    | B1    | В0    |

| 0x07           | PAIE | -  | -  | PAIE5 | PAIE4 | PAIE3 | PAIE2 | PAIE1 | PAIE0 |

Legend: - = unimplemented, read as '0'.

**PAIE0**: = 1, Enable the input change interrupt function of PA0 pin.

= 0, Disable the input change interrupt function of PA0 pin.

**PAIE1**: = 1, Enable the input change interrupt function of PA1 pin.

= 0, Disable the input change interrupt function of PA1 pin.

PAIE2: = 1, Enable the input change interrupt function of PA2 pin.

= 0, Disable the input change interrupt function of PA2 pin.

**PAIE3**: = 1, Enable the input change interrupt function of PA3 pin.

= 0, Disable the input change interrupt function of PA3 pin.

PAIE4: = 1, Enable the input change interrupt function of PA4 pin.

= 0, Disable the input change interrupt function of PA4 pin.

**PAIE5**: = 1, Enable the input change interrupt function of PA5 pin.

= 0, Disable the input change interrupt function of PA5 pin.

#### 2.1.7 PACON (PORTA Interrupt pin-change/edge control Register)

| Read/Write-POR |       | -  | -  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------------|-------|----|----|--------|--------|--------|--------|--------|--------|

| Address        | Name  | В7 | В6 | B5     | B4     | В3     | B2     | B1     | В0     |

| 0x09           | PACON | _  | _  | PACON5 | PACON4 | PACON3 | PACON2 | PACON1 | PACON0 |

Legend: - = unimplemented, read as '0'.

**PACON0**: = 1, Pin-change to interrupt of PA0 pin.

= 0, Falling edge to interrupt of PA0 pin.

**PACON1**: = 1, Pin-change to interrupt of PA1 pin.

= 0, Falling edge to interrupt of PA1 pin.

**PACON2**: = 1, Pin-change to interrupt of PA2 pin.

= 0, Falling edge to interrupt of PA2 pin.

**PACON3**: = 1, Pin-change to interrupt of PA3 pin.

= 0, Falling edge to interrupt of PA3 pin.

**PACON4**: = 1, Pin-change to interrupt of PA4 pin.

= 0, Falling edge to interrupt of PA4 pin.

**PACON5**: = 1, Pin-change to interrupt of PA5 pin.

= 0, Falling edge to interrupt of PA5 pin.

#### 2.1.8 INTEN (Interrupt Mask Register)

| Read/Write-POR |       | R/W-0 | -  | 1  | R/W-0    | R/W-0    | -  | -  | R/W-0 |

|----------------|-------|-------|----|----|----------|----------|----|----|-------|

| Address        | Name  | В7    | В6 | B5 | B4       | В3       | В2 | B1 | В0    |

| 0x0B           | INTEN | GIE   | -  | -  | LVDTSVIE | LVDT20IE | -  | _  | TM0IE |

Legend: - = unimplemented, read as '0'.

TM0IE: Timer0 match interrupt enable bit.

= 1, Enable the Timer0 match interrupt.

= 0, Disable the Timer0 match interrupt.

LVDT20IE: LVDT2.0V interrupt enable bit.

= 1, Enable the LVDT 2.0V falling edge interrupt.

= 0, Disable the LVDT 2.0V falling edge interrupt.

LVDTSVIE: LVDTSV interrupt enable bit.

= 1, Enable the LVDTSV falling edge interrupt.

= 0, Disable the LVDTSV falling edge interrupt.

**GIE**: Global interrupt enable bit.

= 1, Enable all un-masked interrupts.

= 0, Disable all interrupts.

### 2.1.9 INTFLAG (Interrupt Status Register)

| Read/Write-POR |         | -  | R/W-0 | -  | R/W-0    | R/W-0    | -  | -  | R/W-0 |

|----------------|---------|----|-------|----|----------|----------|----|----|-------|

| Address        | Name    | B7 | В6    | B5 | B4       | В3       | B2 | B1 | В0    |

| 0x0C           | INTFLAG | -  | PAIF  | -  | LVDTSVIF | LVDT20IF | -  | -  | TM0IF |

Legend: - = unimplemented, read as '0'.

TM0IF: Timer1 match interrupt flag. Set when TM0 register matches to T0RLD register, reset by software.

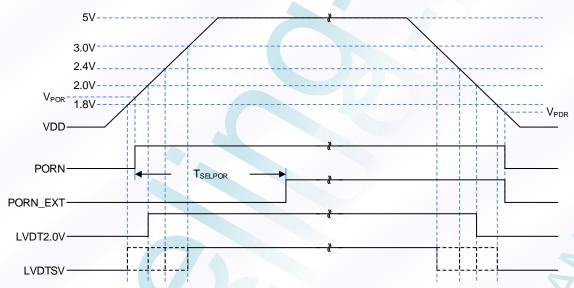

LVDT20IF : LVDT2.0V falling edge interrupt flag, Set when LVDT2.0V falling edge, reset by software.

LVDTSVIF: LVDTSV falling edge interrupt flag, Set when LVDTSV falling edge, reset by software.

PAIF: Port A input change interrupt flag. Set when Port A input changes, reset by software.

### 2.1.10 TM0 (Timer0 Clock/Counter register)

| Read/Write-POR |      | R-0 | R-0                           | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

|----------------|------|-----|-------------------------------|-----|-----|-----|-----|-----|-----|

| Address        | Name | В7  | В6                            | B5  | В4  | В3  | B2  | B1  | В0  |

| 0x0E           | TMØ  |     | 8-bit real time clock/counter |     |     |     |     |     |     |

The Timer0 is an 8-bit timer/counter. The clock source of Timer0 can come from the F<sub>CPU</sub>, F<sub>IRC</sub>, F<sub>SIRC</sub>, or by an external clock source (T0CK pin) defined by TM0CKS<1:0> bits (TM0CON<2:1>). If T0CK pin is selected, the Timer0 is increased by T0CK signal rising edge.

### 2.1.11 TM0CON (Timer0 Control Register)

| Read/Wr | ite-POR | R/W-0 | -  | R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0   | -  |

|---------|---------|-------|----|--------|--------|--------|---------|---------|----|

| Address | Name    | В7    | B6 | B5     | B4     | В3     | B2      | B1      | В0 |

| 0x0F    | TMØCON  | TM0EN | -  | TM0PS2 | TM0PS1 | TM0PS0 | TM0CKS1 | TM0CKS0 | -  |

Legend: - = unimplemented, read as '0'.

TM0CKS1:TM0CKS0: Timer0 clock source selection bits.

| TM0CKS1 | TM0CKS0 | Timer0 clock source                                            |

|---------|---------|----------------------------------------------------------------|

| 0       | 0       | FCPU                                                           |

| 0       | 1       | Firc (16MHz)                                                   |

| 1       | 0       | F <sub>SIRC</sub>                                              |

| 1       | 1       | T0CK (External clock, counter is increased on the rising edge) |

TM0PS2:TM0PS0: Timer0 Pre-scaler selection bits.

| 1 | TM0P | S2:TN | /10PS0 | Timer0 Pre-scaler rate |

|---|------|-------|--------|------------------------|

|   | 0    | 0     | 0      | 1:2                    |

|   | 0    | 0     | 1      | 1:4                    |

| ı | 0    | 1     | 0      | 1:8                    |

|   | 0    | 1     | 1      | 1:16                   |

|   | 1    | 0     | 0      | 1:32                   |

|   | 1    | 0     | 1      | 1:64                   |

| ı | 1    | 1     | 0      | 1:128                  |

|   | 1    | 1     | 1      | 1:256                  |

TM0EN: Timer0 Enable/Disable bit.

= 1, Timer0 Enable.= 0, Timer0 Disable.

### 2.1.12 T0RLD (Timer0 compare Pre-set Register)

| Read/Wr | ite-POR | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

|---------|---------|-------|-------|-------|---------|-------------|-------|-------|-------|

| Address | Name    | В7    | В6    | B5    | B4      | В3          | B2    | B1    | В0    |

| 0x10    | TØRLD   |       |       | TM0   | Compare | Pre-set reg | ister |       |       |

TORLD is Timer0 compare value pre-set register, see section 2.3 for detail description on page 29.

### 2.1.13 WDT (Watch dog Control Register)

| Read/Wr | ite-POR | R/W-1 | R/W-1 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | -    | -  |

|---------|---------|-------|-------|--------|--------|--------|-------|------|----|

| Address | Name    | В7    | В6    | B5     | B4     | В3     | B2    | B1   | В0 |

| 0x11    | WDT     | WDTE  | WDTSL | WDTPS2 | WDTPS1 | WDTPS0 | LVRSL | // - | -  |

Legend: - = unimplemented, read as '0'.

LVRSL: LVR signal select bit.

If device in Green mode:

= 1, LVR signal will wake-up device to normal mode (PC = Next instruction).

= 0, LVR signal will Reset device.

else:

Ignore.

WDTPS2:WDTPS0: Watchdog timer pre-scaler setting

| WDT | PS2 : WD | TPS0 | WDT pre-scaler rate |

|-----|----------|------|---------------------|

| 0   | 0        | 0    | 1:1                 |

| 0   | 0        | 1    | 1:2                 |

| 0   | 1        | 0    | 1:4                 |

| 0   | 1        | 1    | 1:8                 |

| 1   | 0        | 0    | 1:16                |

| 1   | 0        | 1    | 1:32                |

| 1   | 1        | 0    | 1:64                |

| 1   | 1        | 1    | 1:128               |

Note: Watchdog period time-base select by Configuration word.

WDTSL: Watchdog wakeup mode selection bit.

- = 1, Disable WDT wakeup, when the WDT time-out, device will be reset.

- = 0, Enable WDT wakeup, when the WDT time-out, device will be wakeup to normal mode, and execution next instruction

WDTE: Watchdog Timer Enable/ Disable.

= 1, WDT Enable.

= 0, WDT disable.

### 2.1.14 PCON (Power Control Register)

| Read/Write-POR |      | -  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0 | R-#    | R-#    |

|----------------|------|----|--------|-------|--------|--------|-------|--------|--------|

| Address        | Name | B7 | В6     | B5    | B4     | В3     | B2    | B1     | В0     |

| 0x12           | PCON | -  | GRN_MD | LVDIS | RSTSL1 | RSTSL0 | UGMD  | LVDTSV | LVDT20 |

Legend: - = unimplemented, read as '0'.

LVDT20: LVDT 2.0V detect signal.

= 1, VDD > 2.0V.

= 0, VDD  $\leq$  2.0V.

**LVDTSV**: LVDT software selection voltage detection signal.

= 1, VDD > (1.8V, 2.0V, 2.4V or 3.0V).

= 0, VDD ≤ (1.8V, 2.0V, 2.4V or 3.0V). Note: This detect voltage define by BZS register.

**UGMD**: Ultra Green mode select bit.

= 1, SIRC is set to 3.2K<sub>HZ</sub>.

= 0, SIRC set-back 32K<sub>HZ</sub>.

#### RSTSL1:RSTSL0: Reset function select bits.

| RS | STSL1:0 | Reset function description                                 |

|----|---------|------------------------------------------------------------|

| 0  | 0       | POR, PDR, PDRS and WDR signal can be reset device.         |

| 0  | 1       | POR, PDR, PDRS, WDR and LVDTSV signal can be reset device. |

| 1  | 0       | POR, PDR, PDRS, WDR and LVDT20 signal can be reset device. |

| 1  | 1       | POR, PDR, PDRS, WDR and RSTB signal can be reset device.   |

Note: When the POR, PDR, PDRS event occurs, RSTSL<1:0> will be reset to default state. Other event (WDR, LVDTSV, LVDT20V or RSTB) occurs, RSTL<1:0> will remain the last setting.

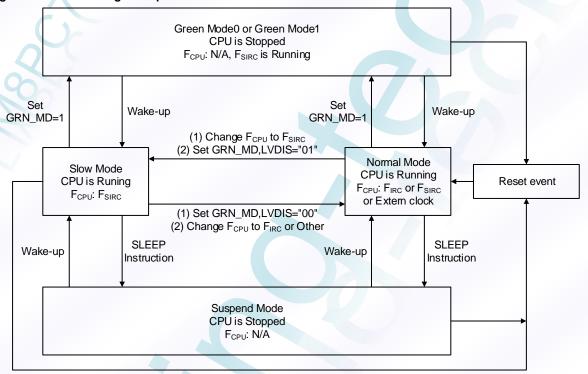

### GRN\_MD:LVDIS: Operation mode select bits.

| GRM_ME | : LVDIS | Operation mode description                                                                        |

|--------|---------|---------------------------------------------------------------------------------------------------|

| 0      | 0       | Normal Mode, and All LVDT20V, LVDTSV circuit are enable.                                          |

|        |         | Slow Mode, and All LVDT20V, LVDTSV circuit are disable.                                           |

| 0      | 1       | $F_{CPU}$ is enable ( $F_{CPU} = F_{SIRC}$ ).                                                     |

|        |         | Note: In this mode, Program must be first Switching F <sub>CPU</sub> clock to F <sub>SIRC</sub> . |

| 1      | 0       | Green Mode 0, and All LVDT20V, LVDTSV circuit are enable.                                         |

|        | U       | FCPU Disable.                                                                                     |

| 1      | 1       | Green Mode 1, and All LVDT20V, LVDTSV circuit are disable.                                        |

| l l    | ı       | F <sub>CPU</sub> Disable.                                                                         |

Note: 1. Operation mode select bit recommended using MOVAR instruction to access.

- 2. Device wake-up from Green mode 0 or Green mode 1, Operation mode select bits will automatically revert to the previous operating mode.

- 3. See section 2.10 for detail description on page 49.

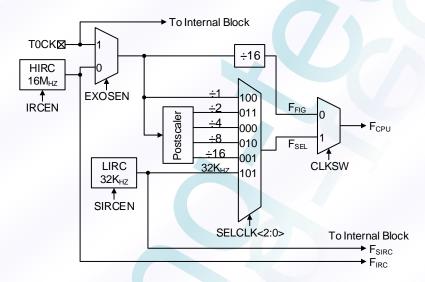

### 2.1.15 CLKCFG (Oscillator and Clock Control Register)

| Read/Write-POR |        | R/W-0   | R/W-0   | R/W-0   | R/W-0 | -            | R/W-1  | R/W-0  | R/W-1 |

|----------------|--------|---------|---------|---------|-------|--------------|--------|--------|-------|

| Address        | Name   | B7      | В6      | B5      | B4    | В3           | B2     | B1     | В0    |

| 0x13           | CLKCFG | SELCLK2 | SELCLK1 | SELCLK0 | CLKSW | / - <b>-</b> | INCODS | EXOSEN | IRCEN |

Legend: - = unimplemented, read as '0'.

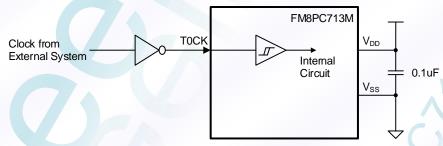

IRCEN: Internal RC Enable bit

= 1, Enable internal RC clock source.

= 0, Disable internal RC clock source (Power down Fire).

Note: Make sure the system clock (FcPu) been switch to external clock source before power down internal

RC.

**EXOSEN**: Internal clock / External clock Source Selection bit

= 1, The clock source is external clock (T0CK).

= 0, The clock source is internal clock (FIRC).

INCODS: Internal clock output Enable bit.

= 1, Disable internal clock output.

= 0, Enable internal RC clock output, the IRC clock is output to XOUT pin.

**CLKSW**: System Clock (FcPU) Selection bit

= 1, CPU Clock is F<sub>SEL</sub>. = 0, CPU Clock is F<sub>FIG</sub>.

**SELCK2:SELCK0**: Clock divider and SIRC selection bits.

| SELC | CK2 : SEI | CKU  | Desci                   | ription    |  |  |  |  |  |

|------|-----------|------|-------------------------|------------|--|--|--|--|--|

| SELC | /NZ . 3EI | LCKU | EXOSEN = 0              | EXOSEN = 1 |  |  |  |  |  |

| 0    | 0         | 0    | F <sub>IRC</sub> /4     | T0CK/4     |  |  |  |  |  |

| 0    | 0         | 1 🛕  | Firc/16                 | T0CK/16    |  |  |  |  |  |

| 0    | 1         | 0    | F <sub>IRC</sub> /8     | T0CK/8     |  |  |  |  |  |

| 0    | 1         | 1    | F <sub>IRC</sub> /2     | T0CK/2     |  |  |  |  |  |

| 1    | 0         | 0    | Firc/1                  | T0CK/1     |  |  |  |  |  |

| 1    | 0         | 1    | SII                     | RC         |  |  |  |  |  |

| 1    | 1         | 0    | No function, don't use. |            |  |  |  |  |  |

| 1    | 1         | 1    |                         |            |  |  |  |  |  |

Note: 1. This control register prohibits direct write value, Need using BSR/BCR instruction.

2. Please refer section 2.12 for detail description on page 55.

### 2.1.16 PWM0CON (PWM0 Control Register 1)

| Read/Write-POR |         | R/W-0   | ı  | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0   | R/W-0   |

|----------------|---------|---------|----|-------|-------|--------|--------|---------|---------|

| Address        | Name    | B7      | В6 | B5    | B4    | В3     | B2     | B1      | В0      |

| 0x14           | PWM0CON | P0INTSL | -  | LPTS0 | ENLP0 | P0CKS1 | P0CKS0 | P00SEL1 | P00SEL0 |

Legend: - = unimplemented, read as '0'.

P00SEL1:P00SEL0: PWM0 / Buzzer0 output channel selection bits.

| P0OSEL1 | : P0OSEL0 | PWM0 / Buzzer0 output Pin         |

|---------|-----------|-----------------------------------|

| 0       | 0         | PWM0 / Buzzer0 output on PA3 pin. |

| 0       | 1         | PWM0 / Buzzer0 output on PA0 pin. |

| 1       | 0         | PWM0 / Buzzer0 output on PA4 pin. |

| 1       | 1         | PWM0 / Buzzer0 output on PA5 pin. |

Note: In differential mode, PA2 has been fixed for the differential output.

POCKS1:POCKS0: PWM0 / Buzzer0 counter clock source selection bits.

| P0CKS1 | : P0CKS0 | PWM0 / Buzzer0 clock source                                         |

|--------|----------|---------------------------------------------------------------------|

| 0      | 0        | Fcpu                                                                |

| 0      | 1        | Firc (16MHz)                                                        |

| 1      | 0        | F <sub>IRC</sub> (16M <sub>HZ</sub> ), PA2 is differential output.* |

| 1      | 1        | T0CK (External clock, counter is increased on the rising edge)      |

Note: POCKS <1:0> = '10' only for differential output mode.

**ENLP0**: Non-overlap for PWM0 differential output.

If P0CKS<1:0> = 10:

- = 1, Disable Non-overlap function.

- = 0, Enable Non-overlap function.

If P0CKS<1:0> = Other:

Ignore.

LPTS0: PWM0 Non-overlap Selection bit

If P0CKS<1:0> = 10:

- = 1, Non-overlap timing > 125nS.

- = 0, Non-overlap timing > 8nS.

If P0CKS<1:0> = Other:

Ignore.

**POINTSL**: PWM0 interrupt event selection bit.

- = 1, Interrupt at PWM0 counter matches to P0TMDTLB and P0TMDTHB register.

- = 0, Interrupt at PWM0 counter matches to P0TMPRLB and P0TMPRHB register.

Note: Set to "1" only for Buzzer / Timer mode. See section 2.4 for detail description on page 29.

### 2.1.17 PWM0CR (PWM0 Control Register 2)

| Rea   | Read/Write-POR |        | R/W-0  |

|-------|----------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Addre | ess            | Name   | B7     | В6     | B5     | B4     | В3     | B2     | B1     | В0     |

| 0x1   | .5             | PWM0CR | PWM0EN | P00UTS | PØTPS2 | P0TPS1 | P0TPS0 | POTMEN | P0TMIE | P0TMIF |

**P0TMIF**: PWM0 interrupt flag, Set when PWM0 compare match, reset by software. See section 2.4 for detail description on page 29.

POTMIE: PWM0 matches interrupt enable bit.

= 1, Enable PWM0 interrupt.= 0, Disable PWM0 interrupt.

POTMEN: PWM0 Enable/Disable bit.

= 1, Enable PWM0. = 0, Disable PWM0.

P0TPS2:P0TPS0: PWM0 pre-scaler selection bits.

| P0TP | S2 : P0 | TPS0 | PWM0 Pre-scaler rate |

|------|---------|------|----------------------|

| 0    | 0       | 0    | 1:1                  |

| 0    | 0       | 1    | 1:2                  |

| 0    | 1       | 0    | 1:4                  |

| 0    | 1       | 1    | 1:8                  |

| 1    | 0       | 0    | 1:16                 |

| 1    | 0       | 1    | 1:32                 |

| 1    | 1       | 0    | 1:64                 |

| 1    | 1       | 1    | 1:128                |

POOUTS: PWM0 Output invert selection bit.

= 1, PWM0 Duty cycle pulse is low (Invert).= 0, PWM0 Duty cycle pulse is high (Normal).

PWM0EN: PWM0 Operation mode selection bit.

= 1, PWM mode.

= 0, Timer / Buzzer mode.

### 2.1.18 P0TMLB and P0TMHB (Low byte and High byte of PWM0 Counter Register)

| Read/Wr | rite-POR | R-0 | R-0                             | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |  |

|---------|----------|-----|---------------------------------|-----|-----|-----|-----|-----|-----|--|

| Address | Name     | В7  | B6                              | B5  | B4  | В3  | B2  | B1  | В0  |  |

| 0x16    | P0TMLB   |     | PWM0 real-time counter low-byte |     |     |     |     |     |     |  |

|         |          |     |                                 |     |     |     |     |     |     |  |

| Read/Wr | rite-POR | R-0                              | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

|---------|----------|----------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Address | Name     | В7                               | B6  | B5  | B4  | В3  | B2  | B1  | В0  |

| 0x18    | РОТМНВ   | PWM0 real-time counter high-byte |     |     |     |     |     |     |     |

The P0TMLB and P0TMHB are PWM0 real-time counter, these register are only read. See section 2.4 for detail description on page 29.

### 2.1.19 POTMDTLB and POTMDTHB (Low byte and High byte of PWM0 Duty cycle Pre-set Register)

| Read/Write-POR |          | R/W-0                               | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|----------------|----------|-------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| Address        | Name     | B7                                  | В6    | B5    | B4    | В3    | B2    | B1    | В0    |  |

| 0x17           | POTMDTLB | PWM0 Duty pre-set low-byte register |       |       |       |       |       |       |       |  |

| Read/Wr | ite-POR  | R/W-0                                | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------|----------|--------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| Address | Name     | В7                                   | В6    | B5    | B4    | В3    | B2    | B1    | В0    |  |

| 0x19    | POTMDTHB | PWM0 Duty pre-set high-byte register |       |       |       |       |       |       |       |  |

In PWM mode, these registers are pre-set duty cycle comparison value register, set these registers can be defined PWM0 duty cycle.

In Timer/Buzzer mode, P0TMLB and P0TMHB increase until the value matches to these register, the P0TMLB and P0TMHB will be reset to "0". See section 2.4 for detail description on page 29.

### 2.1.20 PWM1CON (PWM1 Control Register 1)

| 4 | Read/Wr | ite-POR | R/W-0   | -  | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0   | R/W-0   |

|---|---------|---------|---------|----|-------|-------|--------|--------|---------|---------|

|   | Address | Name    | В7      | В6 | B5    | В4    | В3     | B2     | B1      | В0      |

|   | 0x20    | PWM1CON | P1INTSL | -  | LPTS1 | ENLP1 | P1CKS1 | P1CKS0 | P10SEL1 | P10SEL0 |

Legend: - = unimplemented, read as '0'.

P10SEL1:P10SEL0: PWM1 / Buzzer1 output channel selection bits.

| P1OSEL1 | : P1OSEL0 |    | PWM1 / Buzzer1 output Pin         |

|---------|-----------|----|-----------------------------------|

| 0       | 0         | PW | /M1 / Buzzer1 output on PA4 pin.  |

| 0       | 1         | PW | /M1 / Buzzer1 output on PA0 pin.  |

| 1       | 0         | PW | /M1 / Buzzer1 output on PA3 pin.  |

| 1       | 1         | PW | /M1 / Buzzer1 output on PA5 pin*. |

Note: In differential mode, PA5 has been fixed for the differential output, P1CKS<1:0> = 11 will not be available.

### P1CKS1:P1CKS0: PWM1 / Buzzer1 counter clock source selection bits.

| P1CKS1 | : P1CKS0 | PWM1 / Buzzer1 clock source                                         |

|--------|----------|---------------------------------------------------------------------|

| 0      | 0        | Fcpu                                                                |

| 0      | 1        | Firc (16MHz)                                                        |

| 1      | 0        | F <sub>IRC</sub> (16M <sub>HZ</sub> ), PA5 is differential output.* |

| 1      | 1        | T0CK (External clock, counter is increased on the rising edge)      |

Note: P1CKS <1:0> = '10' only for differential output mode.

**ENLP1**: Non-overlap for PWM1 differential output.

If P1CKS<1:0> = 10:

= 1, Disable Non-overlap function.

= 0, Enable Non-overlap function.

If P1CKS<1:0> = Other:

Ignore.

LPTS1: PWM1 Non-overlap Selection bit

If P1CKS<1:0> = 10:

= 1, Non-overlap timing > 125nS.

= 0, Non-overlap timing > 8nS.

If P1CKS<1:0> = Other:

Ignore.

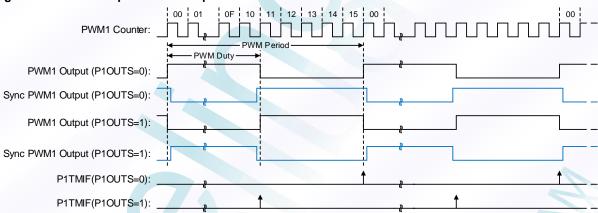

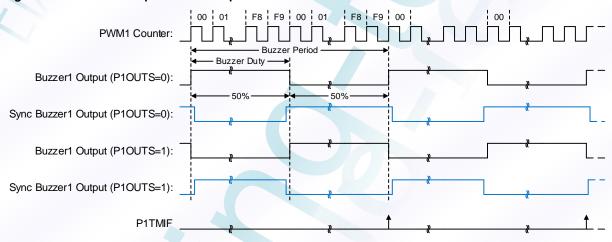

P1INTSL: PWM1 interrupt event selection bit.

= 1, Interrupt at PWM1 counter matches to P1TMDT register.= 0, Interrupt at PWM1 counter matches to P1TMPR register.

Note: Set to "1" only for Buzzer / Timer mode. See section 2.5 for detail description on page 35.

### 2.1.21 PWM1CR (PWM1 Control Register 2)

| Read/Wr | ite-POR | R/W-0  |

|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|

| Address | Name    | В7     | В6     | B5     | B4     | В3     | B2     | B1     | В0     |

| 0x21    | PWM1CR  | PWM1EN | P10UTS | P1TPS2 | P1TPS1 | P1TPS0 | P1TMEN | P1TMIE | P1TMIF |

P1TMIF: PWM1 interrupt flag, Set when PWM1 compare match, reset by software. See section 2.5 for detail

description on page 35.

P1TMIE: PWM1 matches interrupt enable bit.

= 1, Enable PWM1 interrupt.= 0, Disable PWM1 interrupt.

P1TMEN: PWM1 Enable/Disable bit.

= 1, Enable PWM1.= 0, Disable PWM1.

P1TPS2:P1TPS0 : PWM1 pre-scaler selection bits.

| P1TP | S2 : P1 | TPS0 | PWM1 Pre-scaler rate |

|------|---------|------|----------------------|

| 0    | 0       | 0    | 1:1                  |

| 0    | 0       | 1    | 1:2                  |

| 0    | 1       | 0    | 1:4                  |

| 0    | 1       | 1    | 1:8                  |

| 1    | 0       | 0    | 1:16                 |

| 1    | 0       | 1    | 1:32                 |

| 1    | 1       | 0    | 1:64                 |

| 1    | 1       | 1    | 1:128                |

P10UTS: PWM1 Output invert selection bit.

= 1, PWM1 Duty cycle pulse is low (Invert).= 0, PWM1 Duty cycle pulse is high (Normal).

PWM1EN: PWM1 Operation mode selection bit.

= 1, PWM mode.

= 0, Timer / Buzzer mode.

### 2.1.22 P1TM (PWM1 Counter Register)

| Read/Wr | rite-POR | R-0 | R-0                    | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |

|---------|----------|-----|------------------------|-----|-----|-----|-----|-----|-----|

| Address | Name     | B7  | B6                     | B5  | B4  | В3  | B2  | B1  | В0  |

| 0x22    | P1TM     |     | PWM1 real-time counter |     |     |     |     |     |     |

The P1TM is PWM1 real-time counter, this register is only read. See section 2.5 for detail description on page 35.

### 2.1.23 P1TMDT (PWM1 Duty cycle Pre-set Register)

| Read/Wr | rite-POR | R/W-0                      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------|----------|----------------------------|-------|-------|-------|-------|-------|-------|-------|

| Address | Name     | B7                         | В6    | B5    | B4    | В3    | B2    | B1    | В0    |

| 0x23    | P1TMDT   | PWM1 Duty pre-set register |       |       |       |       |       |       |       |

In PWM mode, this register is pre-set duty cycle comparison value register, set this register can be defined PWM1 duty cycle.

In Timer/Buzzer mode, P1TM increase until the value matches to this register, the P1TM will be reset to "0". See section 2.5 for detail description on page 35.

### 2.1.24 BZS (Buzzer Control Register)

| Read/Wr | rite-POR | R/W-0 | R/W-0 | R/W-0  | R/W-0  | _  | -      | -  | -  |

|---------|----------|-------|-------|--------|--------|----|--------|----|----|

| Address | Name     | В7    | В6    | B5     | B4     | В3 | B2     | B1 | В0 |

| 0x24    | BZS      | BZS1  | BZS0  | LVDTS1 | LVDTS0 |    | // - / | -  | -  |

Legend: - = unimplemented, read as '0'.

LVDTS1:LVDTS0: LVDT level Programmable bit

| LVDTS1 | : LVDTS0 | LVDT level                                                       |

|--------|----------|------------------------------------------------------------------|

| 0      | 0        | $V_{DD} \ge 1.8V$ , LVDTSV = 1<br>$V_{DD} \le 1.8V$ , LVDTSV = 0 |

| 0      | 1        | $V_{DD} \ge 2.0V$ , LVDTSV = 1<br>$V_{DD} \le 2.0V$ , LVDTSV = 0 |

| 1      | 0        | $V_{DD} \ge 2.4V$ , LVDTSV = 1<br>$V_{DD} \le 2.4V$ , LVDTSV = 0 |

| 1      | 1        | $V_{DD} \ge 3.0V$ , LVDTSV = 1<br>$V_{DD} \le 3.0V$ , LVDTSV = 0 |

BZS1: Buzzer0 output select bit

= 1, Enable Buzzer output (PWM0EN bit must be "0" (PWM0CR<7>)).

= 0, Disable Buzzer output (Don't care PWM0EN bit).

BZS1: Buzzer1 output select bit

= 1, Enable Buzzer output (PWM1EN bit must be "0" (PWM1CR<7>)).

= 0, Disable Buzzer output (Don't care PWM1EN bit).

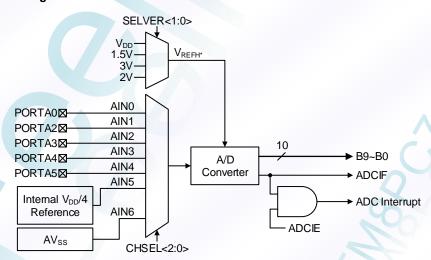

### 2.1.25 ADCON1 (AD Converter Control Register 1)

| Read/Wr | rite-POR | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|----------|-------|-------|--------|--------|--------|--------|--------|--------|

| Address | Name     | В7    | В6    | B5     | B4     | В3     | B2     | B1     | В0     |

| 0x28    | ADCON1   | ADCEN | ADCST | CHSEL2 | CHSEL1 | CHSEL0 | ADCSR2 | ADCSR1 | ADCSR0 |

ADCSR1:ADCSR0: ADC Conversion clock source select bits.

| ADCSR2 | ADCSR1 | ADCSR0 | Conversion clock                                     |

|--------|--------|--------|------------------------------------------------------|

| 0      | 0      | 0      | FcPu/8                                               |

| 0      | 0      | 1      | FcPu/4                                               |

| 0      | 1      | 0      | F <sub>CPU</sub> /2                                  |

| 0      | 1      | 1      | F <sub>CPU</sub> /1 (fastest result, lowest quality) |

| 1      | 0      | 0      | FcPu/16                                              |

| 1      | 0      | 1      | F <sub>CPU</sub> /32                                 |

| 1      | 1      | 0      | FcPu/64                                              |

| 1      | 1      | 1      | F <sub>CPU</sub> /128 (slowest result, best quality) |

Note: 1. This clock is used to control the conversion precision and speed. The precision will be dropped off if faster conversion rate been used. The lowest conversion rate would be recommended in order to acquire most accurate data.

2. Very important, ADC when converting AIN4  $\sim$  AIN0, the ADC clock should not exceed 4MHz!! When the Converting AIN5 (1/4 VDD), the ADC clock should not exceed 1MHz!! See section 2.8.2 for detail description on page 41.

CHS3:CHSEL0: ADC input channel select bits.

| CHSEL2 | CHSEL1 | CHSEL0 | Input channel             |

|--------|--------|--------|---------------------------|

| 0      | 0      | 0      | AIN0 (PA0)                |

| 0      | 0      | 1      | AIN1 (PA2)                |

| 0      | 1      | 0      | AIN2 (PA3)                |

| 0      | 1      | 1      | AIN3 (PA4)                |

| 1      | 0      | 0      | AIN4 (PA5)                |

| 1      | 0      | 1      | AIN5 (V <sub>DD</sub> /4) |

| 1      | 1      | 0      | AIN6 (V <sub>SS</sub> )   |

| 1      | 1      | 1      | No function, do not use.  |

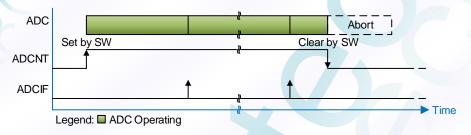

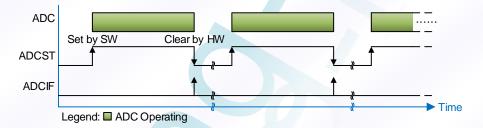

ADCST: AD Conversion start bit.

If ADCNT bit = 1:

Ignore, AD Conversion controlled by H/W.

If ADCNT bit = 0:

= 1, Start AD conversion.

= 0, AD conversion completed.

Note: This bit should be set by software and would be reset by hardware after the ADC end of conversion (ADCNT bit = 0).

ADCEN: ADC module enable bit.

= 1, Enable ADC module.

= 0, Disable ADC module.

### 2.1.26 ADCON2 (AD Converter Control Register 2)

| Read/Wr | rite-POR | R/W-0 | R/W-0 | -  | R/W-0 | R/W-1 | R/W-0  | R/W-0   | R/W-0   |

|---------|----------|-------|-------|----|-------|-------|--------|---------|---------|

| Address | Name     | B7    | В6    | B5 | B4    | В3    | B2     | B1      | В0      |

| 0x29    | ADCON2   | ADCIE | ADCIF | -  | ADCNT | ADCLS | ADCTCK | SELVER1 | SELVER0 |

Legend: - = unimplemented, read as '0'.

SELVER1:SELVER0: ADC Reference voltage select bits.

| SELVER1 | SELVER0 | Internal V <sub>REF</sub> voltage |

|---------|---------|-----------------------------------|

| 0       | 0       | $V_{DD}$                          |

| 0       | 1       | 1.5V                              |

| 1       | 0       | 3V                                |

| 1       | 1       | 2V                                |

**ADCTCK**: ADC Sample rate adjust select bit.

= 1, Sample Rate = AD CLK / 44

= 0, Sample Rate = AD CLK / 34

Note: AD CLK defined by ADCS<2:0>bits (ADCON1<2:0>).

ADCLS: ADC Low sample rate select bit.

= 1, ADC is low sample rate for High solution.

= 0, ADC is normal sample rate.

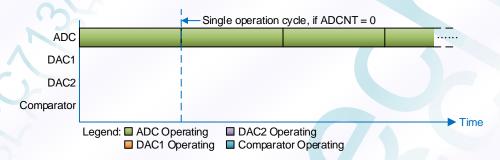

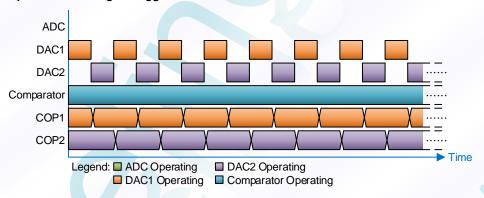

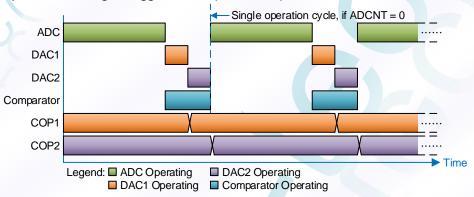

ADCNT: ADC sample mode select bit.

= 1, ADC continues mode.

= 0, Trigger mode, based on ADCST bit.

ADCIF: ADC Interrupt flag. Set when ADC conversion is completed, reset by software.

ADCIE: ADC conversion completed interrupt enable bit.

= 1, Enable interrupt.= 0, Disable interrupt.

### 2.1.27 ADCHB and ADCLB (AD Conversion data high-byte and low-byte Register)

| Read/Wr | rite-POR | R-0  |

|---------|----------|------|------|------|------|------|------|------|------|

| Address | Name     | В7   | B6   | B5   | B4   | В3   | B2   | B1   | В0   |

| 0x30    | ADCHB    | ADB9 | ADB8 | ADB7 | ADB6 | ADB5 | ADB4 | ADB3 | ADB2 |

| Read/Wr | rite-POR |    | M - M | A -           | -  | -  | -  | R-0  | R-0  |

|---------|----------|----|-------|---------------|----|----|----|------|------|

| Address | Name     | B7 | В6    | B5            | B4 | В3 | B2 | B1   | В0   |

| 0x31    | ADCLB    | -  | -     | <i>/</i> // - | -  | -  | -  | ADB1 | ADB0 |

Legend: - = unimplemented, read as '0'.

The ADCHB and ADCLB registers is ADC conversion result. When ADC conversion is completed, the result is loaded into ADCHB and ADCLB, the ADCST bit will be cleared, and the ADCIF bit will be set.

### 2.1.28 ADCON3 (AD Converter Control Register 3)

| Read/Wr | rite-POR | -  | ı  | -  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------|----------|----|----|----|-------|-------|-------|-------|-------|

| Address | Name     | В7 | В6 | B5 | B4    | В3    | B2    | B1    | В0    |

| 0x32    | ADCON3   | -  | -  | -  | INEN4 | INEN3 | INEN2 | INEN1 | INEN0 |

Legend: - = unimplemented, read as '0'.

INEN0: = 1, PA0 is Analog input (AIN0).

= 0, PA0 is Digital input.

**INEN1**: = 1, PA2 is Analog input (AIN1).

= 0, PA2 is Digital input.

INEN2: = 1, PA3 is Analog input (AIN2).

= 0, PA3 is Digital input.

INEN3: = 1, PA4 is Analog input (AIN3).

= 0, PA4 is Digital input.

INEN4: = 1, PA5 is Analog input (AIN4).

= 0, PA5 is Digital input.

### 2.1.29 CMPCON1 (Comparator Control Register 1)

| Read/Wr | rite-POR | R/W-0 | R-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|---------|----------|-------|------|--------|---------|---------|--------|--------|--------|

| Address | Name     | В7    | В6   | B5     | B4      | В3      | B2     | B1     | В0     |

| 0x35    | CMPCON1  | CMPEN | COP1 | CMPIE1 | CMPRIF1 | CMPFIF1 | CMPCS2 | CMPCS1 | CMPCS0 |

CMPCS2:CMPCS0: CN (Comparator Negative) input select bits.

| CMPC | CS2 : CM | PCS0 | Input Channel             |

|------|----------|------|---------------------------|

| 0    | 0        | 0    | AIN0 (PA0)                |

| 0    | 0        | 1    | AIN1 (PA2)                |

| 0    | 1        | 0    | AIN2 (PA3)                |

| 0    | 1        | 1    | AIN3 (PA4)                |

| 1    | 0        | 0    | AIN4 (PA5)                |

| 1    | 0        | 1    | AIN5 (V <sub>DD</sub> /4) |

| 1    | 1        | 0    | AIN6 (V <sub>SS</sub> )   |

| 1    | 1        | 1    | No function, do not use.  |

**CMPFIF1**: Comparator output falling edge interrupt flag. Set when DAC1 voltage < CN (CP<CN), reset by software.

CMPRIF1: Comparator output rising edge interrupt flag. Set when DAC1 voltage > CN (CP>CN), reset by software.

**CMPIE1**: Compare DAC1 interrupt enable bit.

= 1, Enable Compare DAC1 interrupt.

= 0, Disable Compare DAC1 interrupt.

**COP1**: Result of compare with DAC1.

= 1, DAC1 voltage > CN.

= 0, DAC1 voltage < CN.

CMPEN: Comparator Enable/Disable bit.

= 1, Enable comparator.

### = 0, Disable comparator.

### 2.1.30 DACR1HB and DACR1LB (DA Conversion data high-byte and low-byte Register 1)

| Read/Wr | rite-POR | R/W-0  |

|---------|----------|--------|--------|--------|--------|--------|--------|--------|--------|

| Address | Name     | В7     | В6     | B5     | B4     | В3     | B2     | B1     | В0     |

| 0x36    | DACR1HB  | DAC1B9 | DAC1B8 | DAC1B7 | DAC1B6 | DAC1B5 | DAC1B4 | DAC1B3 | DAC1B2 |

| Read/Wr | rite-POR | -  | -  | -  | ı   |     |    | R/W-0  | R/W-0  |

|---------|----------|----|----|----|-----|-----|----|--------|--------|

| Address | Name     | В7 | В6 | B5 | B4  | В3  | B2 | B1     | В0     |

| 0x37    | DACR1LB  | -  | -  | -  | - / | /-/ | -  | DAC1B1 | DAC1B0 |

Legend: - = unimplemented, read as '0'.

These register settings DAC1 output voltage. See 2.9.2.2 for detail description on page 45.

### 2.1.31 CMPCON2 (Comparator Control Register 2)

| Read/Wr | rite-POR | R/W-0   | R-0  | R/W-0  | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|---------|----------|---------|------|--------|---------|---------|---------|---------|---------|

| Address | Name     | В7      | В6   | B5     | B4      | В3      | B2      | B1      | В0      |

| 0x38    | CMPCON2  | CMPINT1 | COP2 | CMPIE2 | CMPRIF2 | CMPFIF2 | CMPINT2 | TOGSEL1 | TOGSEL0 |

Legend: - = unimplemented, read as '0'.

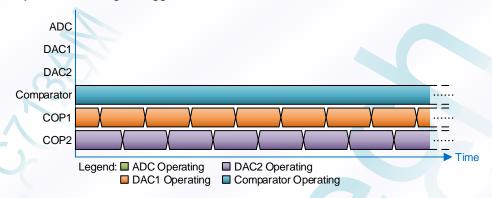

**TOGSEL1:TOGSEL0**: ADC and CMP toggle operation mode selection bits. See 2.9 for detail description on page 43.

CMPINT2: Compare DAC2 interrupt event select bit.

= 1, CMPRIF2 or CMPFIF2 set to 1 to generate interrupt (Comparator output change)

= 0, Only in CMPFIF2 is set to 1 interrupt (Comparator output Falling edge).

**CMPFIF2**: Comparator output falling edge interrupt flag. Set when DAC2 voltage < CN (CP<CN), reset by software.

CMPRIF2: Comparator output rising edge interrupt flag. Set when DAC2 voltage > CN (CP>CN), reset by software.

CMPIE2: Compare DAC2 interrupt enable bit.

= 1, Enable Compare DAC2 interrupt.

= 0, Disable Compare DAC2 interrupt.

COP2: Result of compare with DAC2.

= 1, DAC2 voltage > CN.

= 0, DAC2 voltage < CN.

CMPINT1: Compare DAC1 interrupt event select bit.

= 1, CMPRIF1 or CMPFIF1 set to 1 to generate interrupt (Comparator output change)

= 0, Only in CMPFIF1 is set to 1 interrupt (Comparator output Falling edge).

### 2.1.32 DACR2HB and DACR2LB (DA Conversion data high-byte and low-byte Register 2)

| Read/Wr | rite-POR | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-   | R/W-0  |

|---------|----------|--------|--------|--------|--------|--------|--------|--------|--------|

| Address | Name     | В7     | В6     | B5     | B4     | В3     | B2     | B1     | В0     |

| 0x39    | DACR2HB  | DAC2B9 | DAC2B8 | DAC2B7 | DAC2B6 | DAC2B5 | DAC2B4 | DAC2B3 | DAC2B2 |

| Read/Wr | rite-POR | -  | -  | -  | -  | -  | -  | R/W-0  | R/W-0  |

|---------|----------|----|----|----|----|----|----|--------|--------|

| Address | Name     | В7 | В6 | B5 | B4 | В3 | B2 | B1     | В0     |

| 0x3A    | DACR2LB  | -  | -  | -  | -  | -  | -  | DAC2B1 | DAC2B0 |

Legend: - = unimplemented, read as '0'.

These register settings DAC2 output voltage. See 2.9.2.2 for detail description on page 45.

### 2.1.33 ACC (Accumulator)

| 4 | Read/Wr | rite-POR |             |    |    | R/W | l-x | $A \subseteq A$ |    |    |

|---|---------|----------|-------------|----|----|-----|-----|-----------------|----|----|

|   | Address | Name     | В7          | В6 | B5 | B4  | В3  | B2              | B1 | В0 |

|   | N/A     | ACC      | Accumulator |    |    |     |     |                 |    |    |

Accumulator is an internal data transfer, or instruction operand holding. It cannot be addressed.

### 2.1.34 PAMODE0 and PAMODE1 (Port A mode Control Register 0 & 1)

| Read/Write-POR |         | -  | -  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-1  | R/W-0  |

|----------------|---------|----|----|--------|--------|--------|--------|--------|--------|

| Address        | Name    | В7 | В6 | B5     | B4     | В3     | B2     | B1     | В0     |

| 0x08           | PAMODE0 | _  | 1  | PAMD05 | PAMD04 | PAMD03 | PAMD02 | PAMD01 | PAMD00 |

| Read/Write-POR |         | -  | -  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------------|---------|----|----|--------|--------|--------|--------|--------|--------|

| Address        | Name    | В7 | B6 | B5     | B4     | В3     | B2     | B1     | В0     |

| 0x09           | PAMODE1 |    |    | PAMD15 | PAMD14 | PAMD13 | PAMD12 | PAMD11 | PAMD10 |

Legend: - = unimplemented, read as '0'.

These registers are accessed by the IOST / IOSTR instruction.

PAMODE0 and PAMODE1 is control PORTA pins input / output / driver / sink / pull-up function, each bit in these two registers will control the corresponding PORTA pin, functions is defined as follows:

| Data register (PAx) | MODE1 | MODE0 | Output Drive Strength                     |

|---------------------|-------|-------|-------------------------------------------|

| 1 0                 | 0     | 0     | HI-z(Input mode)                          |

| 1 0                 | 0     | 1     | Pull-High (input mode)                    |

| 1 0                 | 1     | 0     | Pull-High (input mode) Sink (output mode) |

| 1 0                 | 1     | 1     | Normal Drive Sink                         |

### 2.1.35 P0TMPRLB and P0TMPRHB (Low byte and High byte of PWM0 Period cycle Pre-set Register)

| Read/Write-POR |          | R/W-1 | R/W-1                                       | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|----------------|----------|-------|---------------------------------------------|-------|-------|-------|-------|-------|-------|

| Address        | Name     | В7    | В6                                          | B5    | В4    | В3    | B2    | B1    | В0    |

| 0x17           | PØTMPRLB |       | PWM0 Period cycle pre-set low-byte register |       |       |       |       |       |       |

| Read/Write-POR |          | R/W-1 | R/W-1                                        | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|----------------|----------|-------|----------------------------------------------|-------|-------|-------|-------|-------|-------|

| Address        | Name     | В7    | В6                                           | B5    | B4    | В3    | B2    | B1    | В0    |

| 0x19           | PØTMPRHB |       | PWM0 Period cycle pre-set high-byte register |       |       |       |       |       |       |

These registers are accessed by the IOST / IOSTR instruction.

In PWM mode, these registers are pre-set period cycle comparison value register, set these registers can be defined PWM0 period cycle. In Timer/Buzzer mode, these registers are not used, user must be set all bits to "1". See section 2.4 for detail description on page 29.

### 2.1.36 P1TMPR (PWM1 Period cycle Pre-set Register)

| Read/Wr | rite-POR | R/W-1 | R/W-1                              | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|---------|----------|-------|------------------------------------|-------|-------|-------|-------|-------|-------|

| Address | Name     | В7    | В6                                 | B5    | В4    | В3    | B2    | B1    | В0    |

| 0x23    | P1TMPR   |       | PWM1 Period cycle pre-set register |       |       |       |       |       |       |

Accessed by IOST / IOSTR instruction.

In PWM mode, these registers are pre-set period cycle comparison value register, set these registers can be defined PWM1 period cycle. In Timer/Buzzer mode, these registers are not used, user must be set all bits to "1". See section 2.5 for detail description on page 35.

Web site: http://www.feeling-tech.com.tw

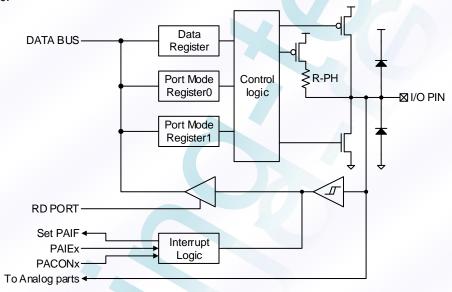

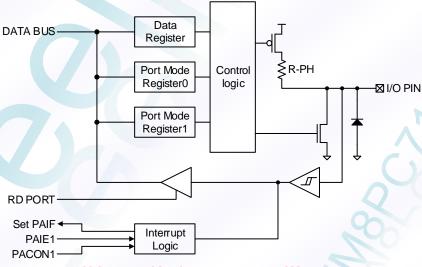

#### 2.2 I/O Ports

Port A is 6-pin bi-directional tristate I/O ports. Please note that PA1 is an input or open-drain output pin.

All I/O pins have corresponding function control registers (PAMODE0, PAMODE1) which can configure these pins as input, output, pull-high and open-drain with pull-high.

PORTA<5:0> also provides the input change interrupt/wake-up function. Each pin has its corresponding input change interrupt/wake-up enable bits (PAIE) to select the input change interrupt/wake-up source. The input change or falling edge function can be selected by PACONx bit (PACON register).

The control register ADCON3 can set several I/Os to analog function. When acting as analog function the pins will read as "0".

Please note, PA1 voltage on this pin must not exceed V<sub>DD</sub>, otherwise it will cause the pin breakdown!!

Figure 2.3: Block Diagram of I/O Pins

PA5 ~ PA2, PA0:

PA1:

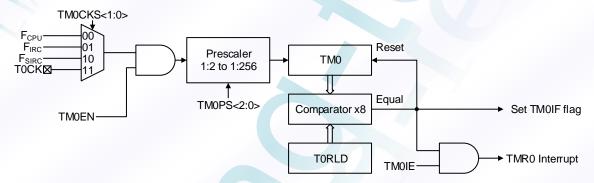

#### 2.3 Timer0

The Timer0 is an 8-bit clock counter with a programmable pre-scaler and an 8-bit compare pre-set register (T0RLD). The clock source of Timer0 comes from the  $F_{CPU}$ ,  $F_{IRC}$ ,  $F_{SIRC}$  or by an external clock source (T0CK pin) defined by TM0CKS<1:0> bits (TM0CON<2:1>).

The option of Timer0 pre-scaler (1:2 to 1:256) is defined by TM0PS2:TM0PS0 (TM0CON<5:3>) bits. The pre-scaler is not be cleared when a value is written to TM0CON register.

The timer increments from 0x00 until it equals the compare pre-set register (TORLD). It then resets to 0x00 at the next increment cycle. The timer interrupt flag (TM0IF, INTFLAG<0>) is set when the timer rollover to 0x00. Please note, do not written 0x00 to compare pre-set register (T0RLD). If written, timer will unable to count.

The timer also has a corresponding interrupt enable bit (TM0IE, INTEN<0>). The timer interrupt can be enabled/disabled by setting/clearing this bit.

The timer is can be turned on and off under software control. When the timer on control bit (TM0EN, TM0CON<7>) is set, the timer is re-initial and increments from the clock source rising edge. When TM0EN is cleared, the timer is turned off.

Figure 2.4: Block Diagram of the Timer0

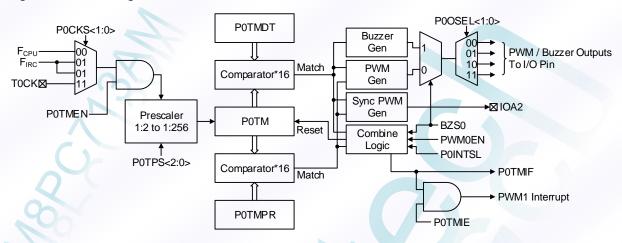

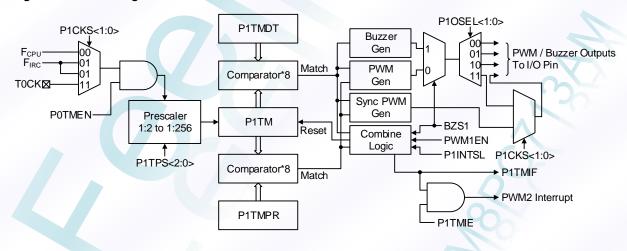

#### 2.4 PWM0 / Buzzer0 / Timer1

The PWM0 module is a 16-bit clock counter with a programmable pre-scaler, and dual 16-bit compare pre-set register. The clock source comes from the F<sub>CPU</sub>, F<sub>IRC</sub> or by an external clock source (T0CK pin) defined by P0CKS<1:0> bits (PWM0CON<3:2>).

The option of PWM0 pre-scaler (1:2 to 1:256) is defined by P0TPS<2:0> (PWM0CR<5:3>) bits. **The pre-scaler is** not be cleared when a value is written to PWM0CR register.

The PWM0 / Buzzer0 output pin can be programmable to PA0, PA3, PA4 or PA5 defined by P0OSEL<1:0> (PWM0CR<5:3>) bits. When I/O is programmed as PWM0 / Buzzer0 output, the corresponding I/O must be set to output mode by program.

The PWM0 module also has a corresponding interrupt enable bit (P0TMIE, PWM0CR<2>). The PWM module interrupt can be enabled/disabled by setting/clearing this bit.

The PWM0 module is can be turned on and off under software control. When the PWM0 enable control bit (P0TMEN, PWM0CR<2>) is set, the PWM0 module is re-initial and increments from the clock source rising edge. When P0TMEN is cleared, the PWM0 module is turned off.

The PWM0 module has three modes of operation; PWM, Buzzer and timer mode, detailed description as follows:

Table 2.1: PWM0 and PWM1 module operating mode

| - |      |        |         | op or area grand and       |

|---|------|--------|---------|----------------------------|

| I | BZSx | PWMxEN | PxINTSL | PWMx module Operating mode |

| I | 0 0  |        | 1       | Timer mode                 |

| I | 0    | 1      | X       | PWM mode                   |

| I | 1 0  |        | 1       | Buzzer mode                |

| ĺ |      | Other  |         | Do not select              |

Figure 2.5: Block Diagram of the PWM0

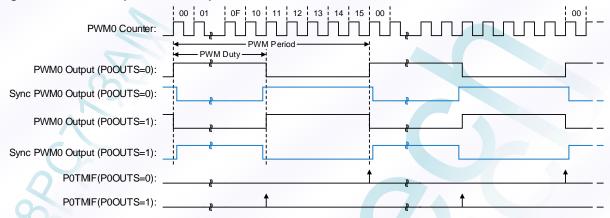

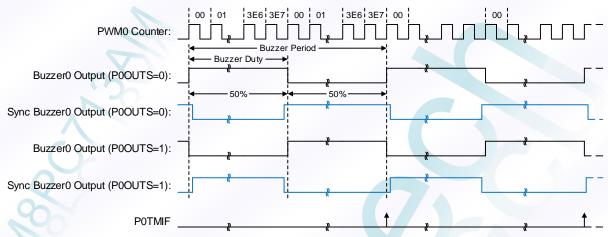

#### 2.4.1 Normal PWM mode

In this mode, PWM0 duty-cycle defined by P0TMDTLB and P0TMDTHB register, Period-cycle defined by P0TMPRLB and P0TMPRHB. Meanwhile, BZS0, PWM0EN and P0INTSL bits must be set to the state specified of Table 2.1. Please note, do not written 0x0000 to compare pre-set register (P0TMPRLB and P0TMPRHB). If written, PWM0 counter will unable to count.

When changing PWM0 Period-cycle or Duty-cycle, the next cycle will load the new settings.

The PWM0 period-cycle time can be calculated as follows:

Period-cycle time of PWM0 =

$$\frac{\text{(P0TMPR+1)} * \text{PWM0 Pre-scaler rate}}{\text{PWM0 Clock source frequency}}$$

or

$$\text{P0TMPR} = \frac{\text{Period-cycle time} * \text{PWM0 Clock source frequency}}{\text{PWM0 Pre-scaler rate}} - 1$$

The PWM0 duty-cycle time can be calculated as follows:

Duty-cycle time of PWM0 =

$$\frac{\text{P0TMDT * PWM0 Pre-scaler rate}}{\text{PWM0 Clock source frequency}}$$

or

$$\text{P0TMDT} = \frac{\text{Duty-cycle time * PWM0 Clock source frequency}}{\text{PWM0 Pre-scaler rate}}$$

Please note: The PWM duty-cycle time must be less than PWM period-cycle time.

### Figure 2.6: PWM0 Output and Interrupt event Waveform

### Example 2.2: PWM0 Setting (BZS0=0, PWM0EN=1, P0INTSL=x)

| ASM | Langua | ae | Code |

|-----|--------|----|------|

|     |        |    |      |

| #include | <8PC713A    | AM.ASH>               |                                                                      |

|----------|-------------|-----------------------|----------------------------------------------------------------------|

|          |             |                       |                                                                      |

|          | MOVIA       | 0x05                  | ; PWM interrupt occur at end of period-cycle                         |

|          |             |                       | ; (Occur at end of duty-cycle is 0x85)                               |

|          | MOVAR       | PWM0CON               | ; Clock source=F <sub>IRC</sub> 16M <sub>HZ</sub> , Output Pin = PA0 |

|          |             |                       |                                                                      |

|          | MOVIA       | 0xA2                  | ; PWM mode, No-Invert, Pre-scaler=1:16,                              |

|          | MOVAR       | PWM0CR                | ; Enable interrupt (Non-interrupt is 0xA0)                           |

|          |             |                       |                                                                      |

|          | MOVIA       | 0x10                  |                                                                      |

|          | MOVAR       | P0TMDTLB              |                                                                      |

|          | MOVIA       | 0x00                  | ; Set Duty cycle Pre-set=0x0010                                      |

|          | MOVAR       | P0TMDTHB              | ; Duty time = 0x0010*16*1/16M <sub>HZ</sub> = 16uS                   |

|          |             |                       |                                                                      |

|          | MOVIA       | 0x15                  |                                                                      |

|          | MOVAR       | P0TMPRLB              |                                                                      |

|          | MOVIA       | 0x00                  | ; Set Period cycle Pre-set=0x0015                                    |

|          | MOVAR       | P0TMPRHB              | ; Duty time = (0x0015+1)*16*1/16M <sub>HZ</sub> = 21uS               |

|          |             |                       |                                                                      |

|          | BSR         | PWM0CR,P0TMEN_B       | ; Start PWM0                                                         |

|          | //Interrupt | setting, not required |                                                                      |

|          | BSR         | INTEN,GIE_B           | ; Enable Global interrupt                                            |

|          |             |                       |                                                                      |

### C Language Code